Intel готова решить проблему дефицита мощностей TSMC по упаковке чипов

Несмотря на усилия TSMC по кратному увеличению производственных мощностей, связанных с упаковкой чипов по методу CoWoS, принято считать, что именно они являются «узким местом» при производстве чипов для ускорителей вычислений NVIDIA. Представители Intel в интервью EE Times и группе прочих журналистов признались, что компания готова составить конкуренцию TSMC в сфере передовых методов упаковки чипов.

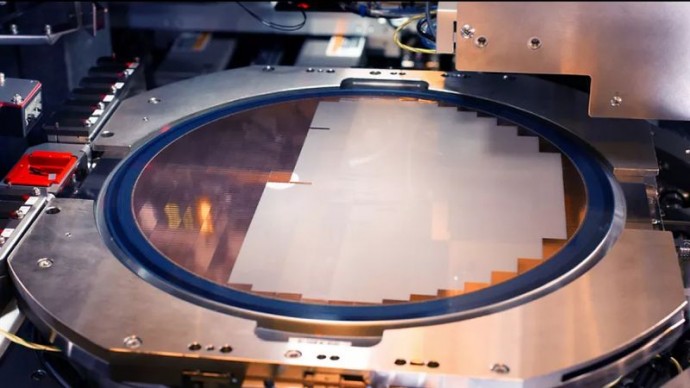

Исторически контрактные производители чипов отдавали приоритет увеличению плотности размещения транзисторов на кристаллах микросхем за счёт освоения более совершенных технологий обработки кремниевых пластин. Со временем прогресс в этой сфере стал упираться в естественные физические пределы, поэтому производители полупроводниковых компонентов начали задумываться о других способах увеличения количества транзисторов. Многочиповые компоненты стали ответом на этот вопрос, но соответствующие производственные линии пока отстают в темпах развития от потребностей рынка.

Intel даёт понять, что её компетенции в сфере упаковки чипов ничем не уступают TSMC. По крайней мере, специалистам Intel уже удалось без особых проблем портировать на свои технологии проекты клиентов, которые ранее использовали CoWoS в исполнении TSMC. В большинстве случаев фирменные технологии Foveros и EMIB позволяют заменить услуги TSMC без потери для потребительских качеств компонентов, как поясняют представители Intel. Впрочем, прямого ответа на вопрос о готовности Intel выпускать чипы для NVIDIA представители первой из компаний при этом не дают. Зато они намекают, что в ближайшие пару лет освоят упаковку чипов по методу EMIB-T, который подразумевает использование межслойных соединений и позволит усложнить пространственную компоновку выпускаемых чипов. По сути, она реально станет трёхмерной.